Hangzhou Xuhong Technology Co.,Ltd

EN

中文

1、 Description

S. EDP-LVDS V1.5 is a signal adapter board mainly used to convert EDP signals into LVDS signals,

The maximum resolution can be supported up to 1920 * 1200. The product can be applied to displays, industrial control PCs, Android all-in-one machines, advertising machines In the field of desktop systems, EDP input needs to comply with the EDP/DP v1.2a or v1.1a specifications; EDP resolution input support is strong Control input mode and EDID configuration mode.

① Forced input mode: The motherboard end EDP OUT forces the output resolution, and the adapter board converts the corresponding LVDS resolution.

② EDID configuration mode: The adapter board has an built-in EDID, and the motherboard reads the internal EDID resolution of the adapter board through EDP,The motherboard EDP outputs the EDID resolution, and the adapter board converts to the corresponding LVDS resolution (requiring the motherboard to support its own EDIDl output resolution)

2. Features

Features ( EPD/DP RX ):(最大支持 2LANE 输入)

• Compliant to EDP/DP v1.2a and v1.1a

• Supports Main Link operation with one or two lanes)

•Supports Main Link rate: Reduced Bit Rate (1.62 Gbit/s) and High Bit Rate (2.7 Gbit/s)

•Supports 1 Mbit/s AUX channel •Supports Native AUX and I2C-over-AUX transactions

•Supports down spreading to minimize EMI

•Integrated 50 termination resistors provide impedance matching on both Main Link lanes and AUX channel

•High performance Auto Receive Equalization enabling optimal channel compensation, device placement flexibility and power saving at CPU/GPU

•Supports Full Link training

Features ( LVDS TX):

• Compatible with ANSI/TIA/EIA-644-A-2001 standard

• Supports RGB data packing as per JEIDA and VESA data formats

• Supports pixel clock frequency from 6 MHz to 112 MHz

• Supports single LVDS bus operation up to 112 mega pixels per second

• S upports dual LVDS bus operation up to 224 mega pixels per second S.EDP-LVDS.V1.5-SPECIFICATION 2

• Supports color depth options: 18 bpp(6bit), 24 bpp(8bit) • Programmable center spreading of pixel clock frequency to minimize EMI

• Supports 1920*1200 at 60 Hz resolution in dual LVDS bus mode

• Programmable LVDS signal swing to pre-compensate for channel attenuation or allow for power saving

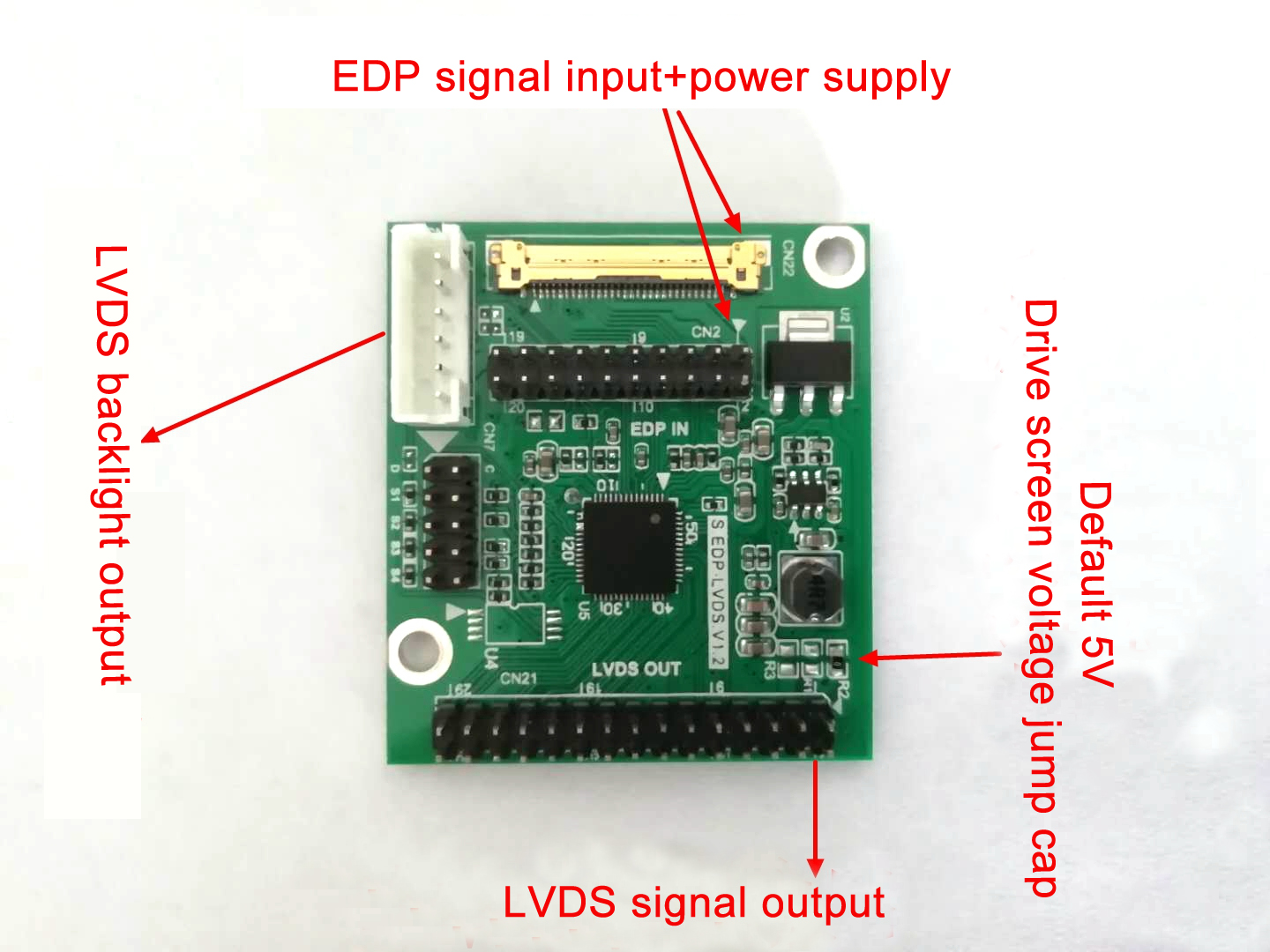

Product appearance

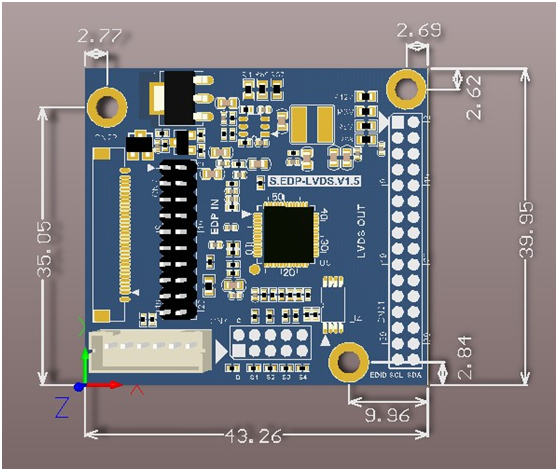

Mechanical Dimension

Configuration & General Precautions

• Relative humidity: ≤ 80%.

• Storage temperature: -20~60°C.

• Operation temperature: -20~60°C.

• Protect the board from static electricity in case of damage to the IC.

• Keep the board away from conductor when it is working.

• Don’t wire in the board to power supply before panel is correctly connected.